ICESugar-Placa de desarrollo FPGA, RISC-V de código abierto, ICE40UP5k, Icebreaker Fomu

Color

Descripción

Lista de envío

● Placa DE DESARROLLO iCESugar * 1

● 1 Cable de *

Documentación

● Repo iCESugar

http://github.com/wuxx/icesugar

● Cadena de herramientas RTL

http:// www. Clifford. AT/icestorm/

● Firmware toolchain

https:// Xpack. Github. IO/riscv-none-embed-gcc/install/

● Ejemplos

https://github.com/damdoy/ice40_ultraplus_examples

https://github.com/icebreaker-fpga/icebreaker-examples

● SpinalHDL

https:// spinalhdl. Github. IO/SpinalDoc-RTD/SpinalHDL/Getting % 20Started/index.html

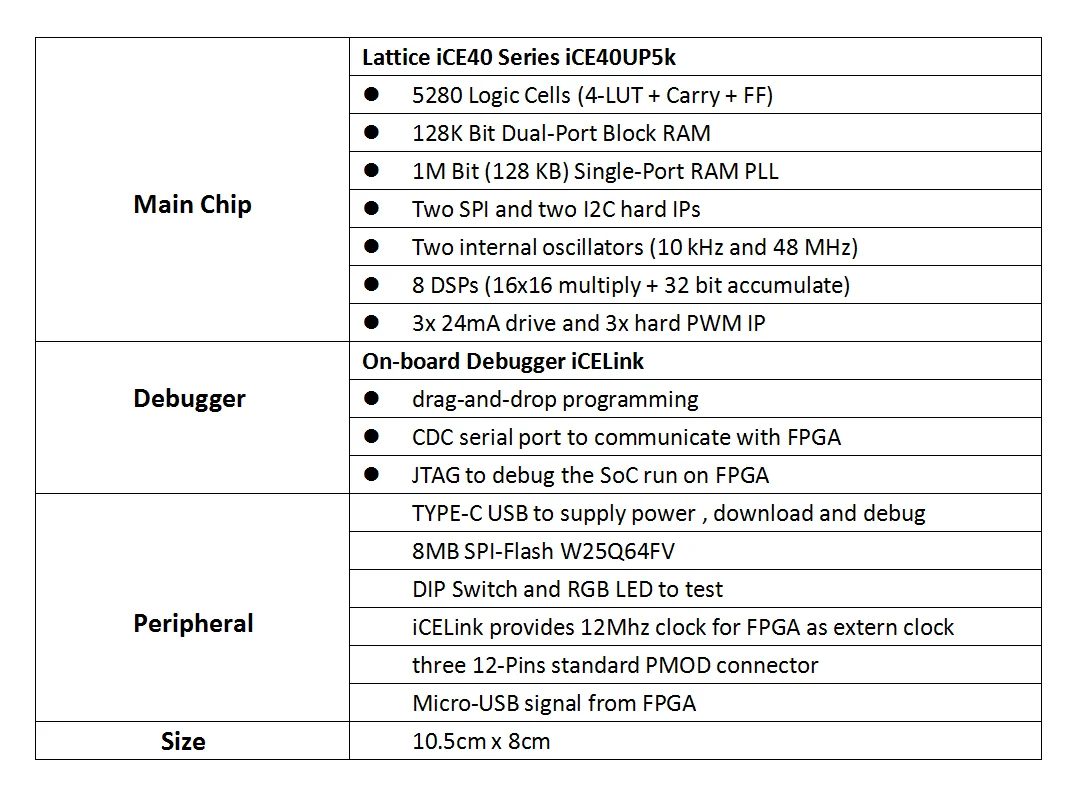

Especificación

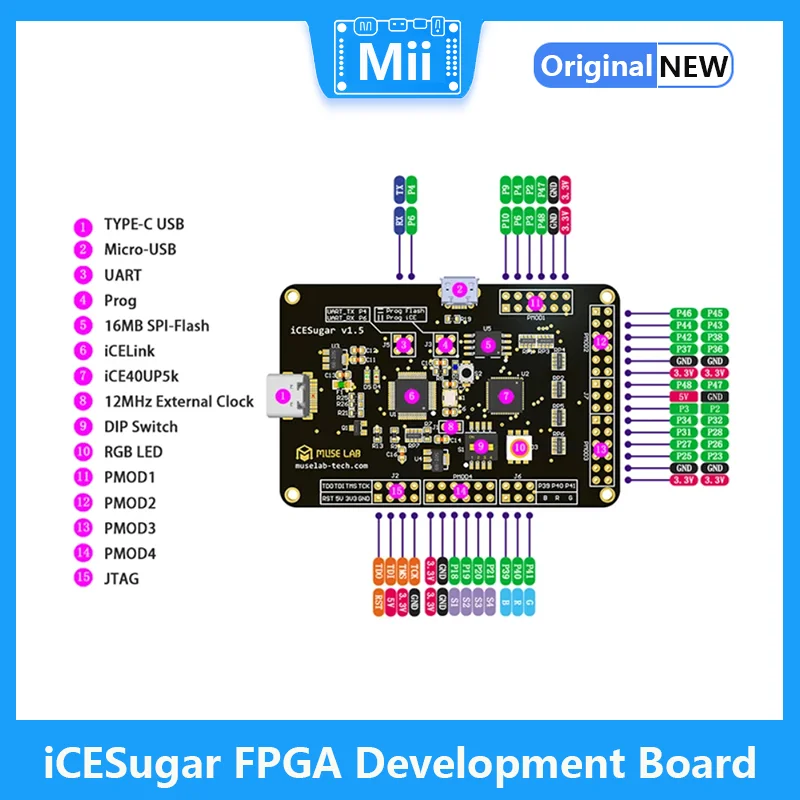

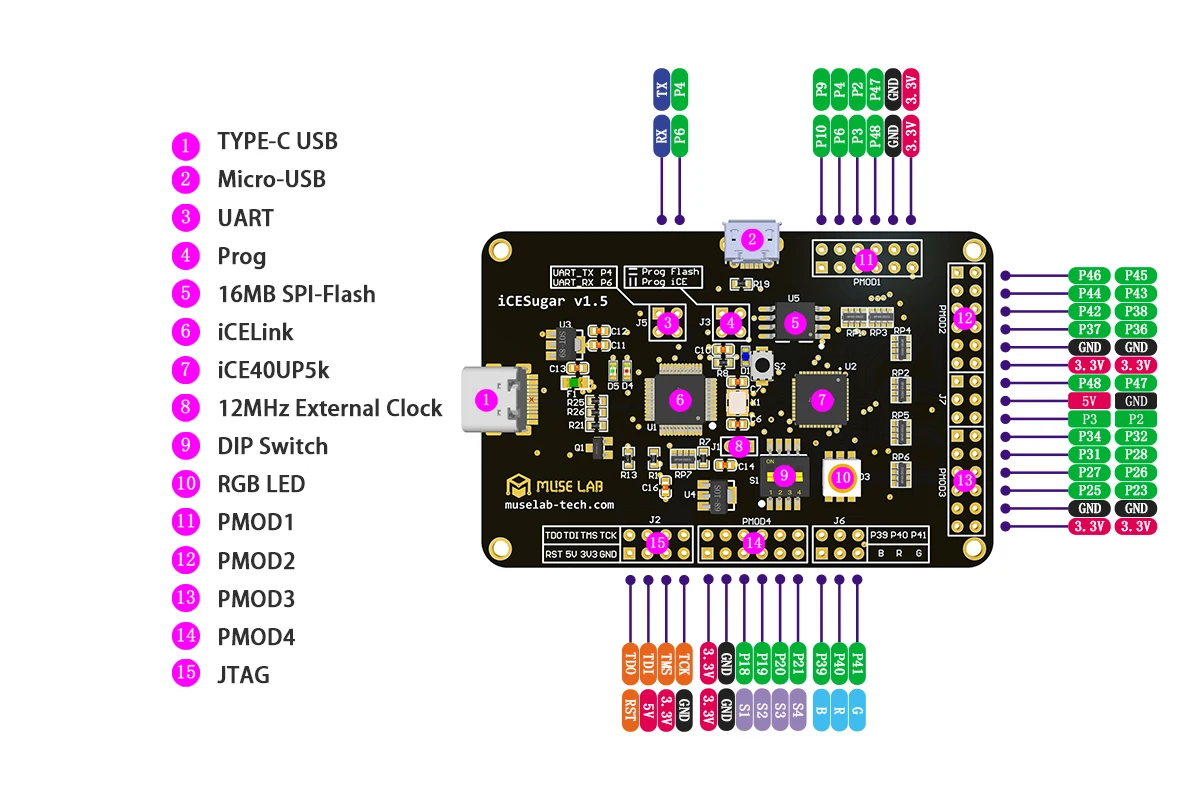

Diagrama

Características

● Chip principal iCE40UP5k, 5280 LUT/128KB SRAM/PLL/ SPI/I2C/DSP/PWM

● Depurador iCELink integrado, compatible con programación de arrastrar y soltar, puerto serie USB CDC y JTAG

● Conduce todo el IO con conector PMOD estándar y puede conectarse con otros dispositivos PMOD

● Utiliza totalmente la cadena de herramientas de código abierto para desarrollar

● SPI-Flash incorporado de 8MB y compatible con DUAL/QUAD SPI y QPI

Introducción

ICESugar es una placa de desarrollo FPGA de código abierto basada en Lattice iCE40UP5k diseñada y fabricada por Muse Lab. Aunque es pequeño y exquisito, Contiene ricos recursos periféricos a bordo que incluyen LED RGB, Switch,TYPE-C-USB, Micro-USB. La mayoría de los IO salen mediante un conector PMOD estándar y se pueden conectar con otros dispositivos PMOD. Además, tiene un depurador integrado llamado iCELink que se basa en ARM Mbed DAPLink. Puede arrastrar el flujo de bits de FPGA al disco virtual para programar con gran comodidad, ya que iCELink admite la programación de arrastrar y soltar, el puerto serie USB CDC y JTAG.